# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

Volume 1: Basic Architecture

**NOTE:** The Intel® 64 and IA-32 Architectures Software Developer's Manual consists of five volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-M, Order Number 253666; Instruction Set Reference N-Z, Order Number 253667; System Programming Guide, Part 1, Order Number 253668; System Programming Guide, Part 2, Order Number 253669. Refer to all five volumes when evaluating your design needs.

Order Number: 253665-034US March 2010 This chapter describes the basic execution environment of an Intel 64 or IA-32 processor as seen by assembly-language programmers. It describes how the processor executes instructions and how it stores and manipulates data. The execution environment described here includes memory (the address space), general-purpose data registers, segment registers, the flag register, and the instruction pointer register.

# 3.1 MODES OF OPERATION

The IA-32 architecture supports three basic operating modes: protected mode, realaddress mode, and system management mode. The operating mode determines which instructions and architectural features are accessible:

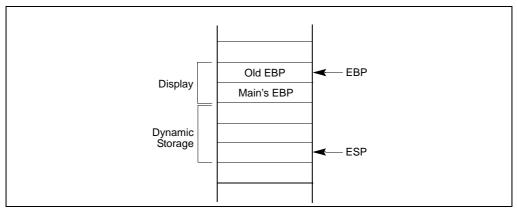

- **Protected mode** This mode is the native state of the processor. Among the capabilities of protected mode is the ability to directly execute "real-address mode" 8086 software in a protected, multi-tasking environment. This feature is called **virtual-8086 mode**, although it is not actually a processor mode. Virtual-8086 mode is actually a protected mode attribute that can be enabled for any task.

- **Real-address mode** This mode implements the programming environment of the Intel 8086 processor with extensions (such as the ability to switch to protected or system management mode). The processor is placed in real-address mode following power-up or a reset.

- System management mode (SMM) This mode provides an operating system or executive with a transparent mechanism for implementing platform-specific functions such as power management and system security. The processor enters SMM when the external SMM interrupt pin (SMI#) is activated or an SMI is received from the advanced programmable interrupt controller (APIC).

In SMM, the processor switches to a separate address space while saving the basic context of the currently running program or task. SMM-specific code may then be executed transparently. Upon returning from SMM, the processor is placed back into its state prior to the system management interrupt. SMM was introduced with the Intel386<sup>™</sup> SL and Intel486<sup>™</sup> SL processors and became a standard IA-32 feature with the Pentium processor family.

# 3.1.1 Intel<sup>®</sup> 64 Architecture

Intel 64 architecture adds IA-32e mode. IA-32e mode has two sub-modes. These are:

Compatibility mode (sub-mode of IA-32e mode) — Compatibility mode permits most legacy 16-bit and 32-bit applications to run without re-compilation under a 64-bit operating system. For brevity, the compatibility sub-mode is referred to as compatibility mode in IA-32 architecture. The execution environment of compatibility mode is the same as described in Section 3.2. Compatibility mode also supports all of the privilege levels that are supported in 64-bit and protected modes. Legacy applications that run in Virtual 8086 mode or use hardware task management will not work in this mode.

Compatibility mode is enabled by the operating system (OS) on a code segment basis. This means that a single 64-bit OS can support 64-bit applications running in 64-bit mode and support legacy 32-bit applications (not recompiled for 64-bits) running in compatibility mode.

Compatibility mode is similar to 32-bit protected mode. Applications access only the first 4 GByte of linear-address space. Compatibility mode uses 16-bit and 32-bit address and operand sizes. Like protected mode, this mode allows applications to access physical memory greater than 4 GByte using PAE (Physical Address Extensions).

• 64-bit mode (sub-mode of IA-32e mode) — This mode enables a 64-bit operating system to run applications written to access 64-bit linear address space. For brevity, the 64-bit sub-mode is referred to as 64-bit mode in IA-32 architecture.

64-bit mode extends the number of general purpose registers and SIMD extension registers from 8 to 16. General purpose registers are widened to 64 bits. The mode also introduces a new opcode prefix (REX) to access the register extensions. See Section 3.2.1 for a detailed description.

64-bit mode is enabled by the operating system on a code-segment basis. Its default address size is 64 bits and its default operand size is 32 bits. The default operand size can be overridden on an instruction-by-instruction basis using a REX opcode prefix in conjunction with an operand size override prefix.

REX prefixes allow a 64-bit operand to be specified when operating in 64-bit mode. By using this mechanism, many existing instructions have been promoted to allow the use of 64-bit registers and 64-bit addresses.

# 3.2 OVERVIEW OF THE BASIC EXECUTION ENVIRONMENT

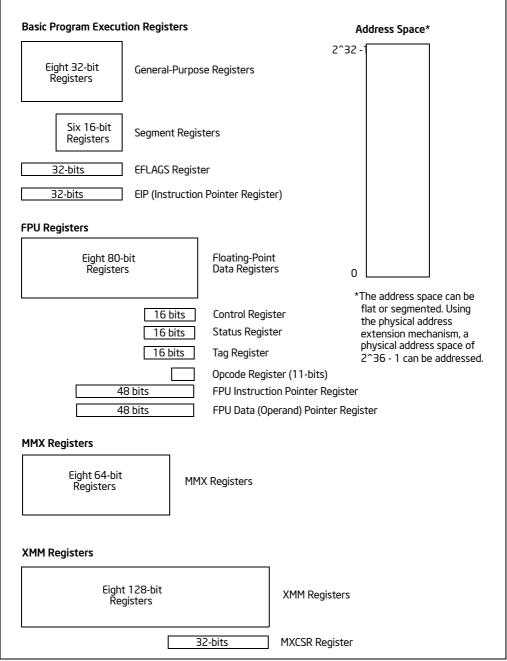

Any program or task running on an IA-32 processor is given a set of resources for executing instructions and for storing code, data, and state information. These

resources (described briefly in the following paragraphs and shown in Figure 3-1) make up the basic execution environment for an IA-32 processor.

An Intel 64 processor supports the basic execution environment of an IA-32 processor, and a similar environment under IA-32e mode that can execute 64-bit programs (64-bit sub-mode) and 32-bit programs (compatibility sub-mode).

The basic execution environment is used jointly by the application programs and the operating system or executive running on the processor.

- Address space Any task or program running on an IA-32 processor can address a linear address space of up to 4 GBytes (2<sup>32</sup> bytes) and a physical address space of up to 64 GBytes (2<sup>36</sup> bytes). See Section 3.3.6, "Extended Physical Addressing in Protected Mode," for more information about addressing an address space greater than 4 GBytes.

- **Basic program execution registers** The eight general-purpose registers, the six segment registers, the EFLAGS register, and the EIP (instruction pointer) register comprise a basic execution environment in which to execute a set of general-purpose instructions. These instructions perform basic integer arithmetic on byte, word, and doubleword integers, handle program flow control, operate on bit and byte strings, and address memory. See Section 3.4, "Basic Program Execution Registers," for more information about these registers.

- x87 FPU registers The eight x87 FPU data registers, the x87 FPU control register, the status register, the x87 FPU instruction pointer register, the x87 FPU operand (data) pointer register, the x87 FPU tag register, and the x87 FPU opcode register provide an execution environment for operating on single-precision, double-precision, and double extended-precision floating-point values, word integers, doubleword integers, quadword integers, and binary coded decimal (BCD) values. See Section 8.1, "x87 FPU Execution Environment," for more information about these registers.

- MMX registers The eight MMX registers support execution of singleinstruction, multiple-data (SIMD) operations on 64-bit packed byte, word, and doubleword integers. See Section 9.2, "The MMX Technology Programming Environment," for more information about these registers.

- XMM registers The eight XMM data registers and the MXCSR register support execution of SIMD operations on 128-bit packed single-precision and double-precision floating-point values and on 128-bit packed byte, word, doubleword, and quadword integers. See Section 10.2, "SSE Programming Environment," for more information about these registers.

Figure 3-1. IA-32 Basic Execution Environment for Non-64-bit Modes

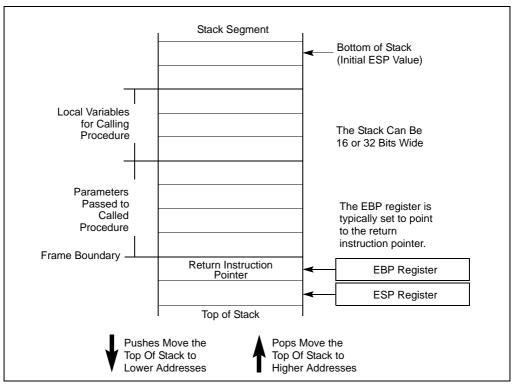

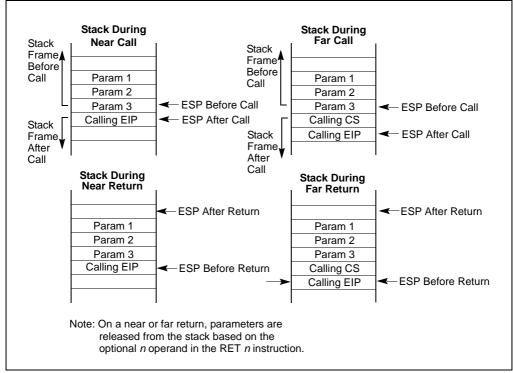

• Stack — To support procedure or subroutine calls and the passing of parameters between procedures or subroutines, a stack and stack management resources are included in the execution environment. The stack (not shown in Figure 3-1) is located in memory. See Section 6.2, "Stacks," for more information about stack structure.

In addition to the resources provided in the basic execution environment, the IA-32 architecture provides the following resources as part of its system-level architecture. They provide extensive support for operating-system and system-development software. Except for the I/O ports, the system resources are described in detail in the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volumes 3A & 3B.*

- **I/O ports** The IA-32 architecture supports a transfers of data to and from input/output (I/O) ports. See Chapter 13, "Input/Output," in this volume.

- **Control registers** The five control registers (CR0 through CR4) determine the operating mode of the processor and the characteristics of the currently executing task. See Chapter 2, "System Architecture Overview," in the *Intel® 64* and *IA-32 Architectures Software Developer's Manual, Volume 3A.*

- Memory management registers The GDTR, IDTR, task register, and LDTR specify the locations of data structures used in protected mode memory management. See Chapter 2, "System Architecture Overview," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

- **Debug registers** The debug registers (DR0 through DR7) control and allow monitoring of the processor's debugging operations. See in the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B.*

- Memory type range registers (MTRRs) The MTRRs are used to assign memory types to regions of memory. See the sections on MTRRs in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volumes 3A & 3B.

- Machine specific registers (MSRs) The processor provides a variety of machine specific registers that are used to control and report on processor performance. Virtually all MSRs handle system related functions and are not accessible to an application program. One exception to this rule is the timestamp counter. The MSRs are described in Appendix B, "Model-Specific Registers (MSRs)," of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B.

- Machine check registers The machine check registers consist of a set of control, status, and error-reporting MSRs that are used to detect and report on hardware (machine) errors. See Chapter 15, "Machine-Check Architecture," of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

- Performance monitoring counters The performance monitoring counters allow processor performance events to be monitored. See Chapter 20, "Introduction to Virtual-Machine Extensions," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B.

The remainder of this chapter describes the organization of memory and the address space, the basic program execution registers, and addressing modes. Refer to the

following chapters in this volume for descriptions of the other program execution resources shown in Figure 3-1:

- x87 FPU registers See Chapter 8, "Programming with the x87 FPU."

- MMX Registers See Chapter 9, "Programming with Intel® MMX™ Technology."

- XMM registers See Chapter 10, "Programming with Streaming SIMD Extensions (SSE)," Chapter 11, "Programming with Streaming SIMD Extensions 2 (SSE2)," and Chapter 12, "Programming with SSE3, SSSE3, SSE4 and AESNI."

- Stack implementation and procedure calls See Chapter 6, "Procedure Calls, Interrupts, and Exceptions."

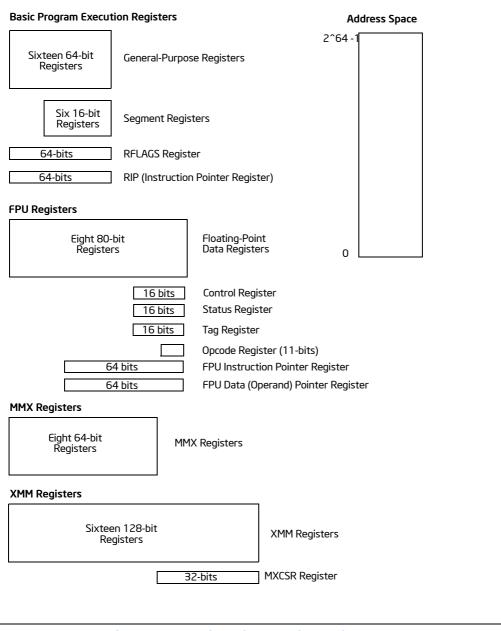

## 3.2.1 64-Bit Mode Execution Environment

The execution environment for 64-bit mode is similar to that described in Section 3.2. The following paragraphs describe the differences that apply.

- Address space A task or program running in 64-bit mode on an IA-32 processor can address linear address space of up to 2<sup>64</sup> bytes (subject to the canonical addressing requirement described in Section 3.3.7.1) and physical address space of up to 2<sup>40</sup> bytes. Software can query CPUID for the physical address size supported by a processor.

- **Basic program execution registers** The number of general-purpose registers (GPRs) available is 16. GPRs are 64-bits wide and they support operations on byte, word, doubleword and quadword integers. Accessing byte registers is done uniformly to the lowest 8 bits. The instruction pointer register becomes 64 bits. The EFLAGS register is extended to 64 bits wide, and is referred to as the RFLAGS register. The upper 32 bits of RFLAGS is reserved. The lower 32 bits of RFLAGS is the same as EFLAGS. See Figure 3-2.

- XMM registers There are 16 XMM data registers for SIMD operations. See Section 10.2, "SSE Programming Environment," for more information about these registers.

- **Stack** The stack pointer size is 64 bits. Stack size is not controlled by a bit in the SS descriptor (as it is in non-64-bit modes) nor can the pointer size be overridden by an instruction prefix.

- **Control registers** Control registers expand to 64 bits. A new control register (the task priority register: CR8 or TPR) has been added. See Chapter 2, "Intel® 64 and IA-32 Architectures," in this volume.

- **Debug registers** Debug registers expand to 64 bits. See Chapter 16, "Debugging, Branch Profiles and Time-Stamp Counter," in the *Intel®* 64 and *IA-32 Architectures Software Developer's Manual, Volume 3A.*

- **Descriptor table registers** The global descriptor table register (GDTR) and interrupt descriptor table register (IDTR) expand to 10 bytes so that they can

hold a full 64-bit base address. The local descriptor table register (LDTR) and the task register (TR) also expand to hold a full 64-bit base address.

Figure 3-2. 64-Bit Mode Execution Environment

# 3.3 MEMORY ORGANIZATION

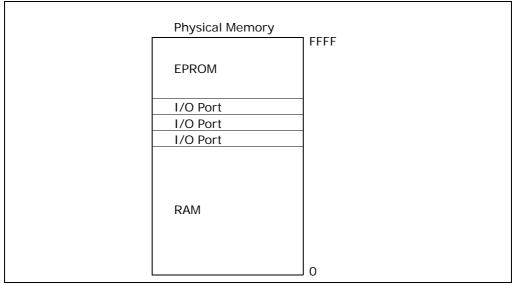

The memory that the processor addresses on its bus is called **physical memory**. Physical memory is organized as a sequence of 8-bit bytes. Each byte is assigned a unique address, called a **physical address**. The **physical address space** ranges from zero to a maximum of  $2^{36} - 1$  (64 GBytes) if the processor does not support Intel 64 architecture. Intel 64 architecture introduces a changes in physical and linear address space; these are described in Section 3.3.3, Section 3.3.4, and Section 3.3.7.

Virtually any operating system or executive designed to work with an IA-32 or Intel 64 processor will use the processor's memory management facilities to access memory. These facilities provide features such as segmentation and paging, which allow memory to be managed efficiently and reliably. Memory management is described in detail in Chapter 3, "Protected-Mode Memory Management," in the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.* The following paragraphs describe the basic methods of addressing memory when memory management is used.

# 3.3.1 IA-32 Memory Models

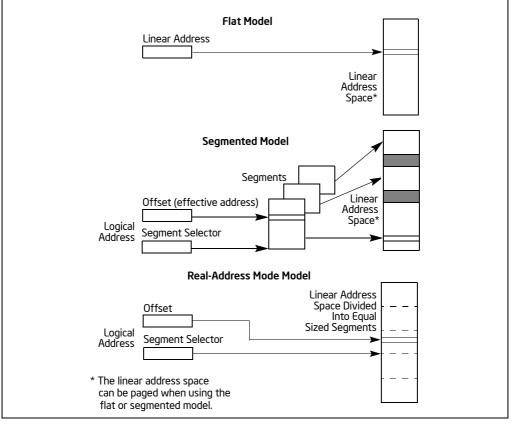

When employing the processor's memory management facilities, programs do not directly address physical memory. Instead, they access memory using one of three memory models: flat, segmented, or real address mode:

- Flat memory model Memory appears to a program as a single, continuous address space (Figure 3-3). This space is called a **linear address space**. Code, data, and stacks are all contained in this address space. Linear address space is byte addressable, with addresses running contiguously from 0 to 2<sup>32</sup> 1 (if not in 64-bit mode). An address for any byte in linear address space is called a **linear address**.

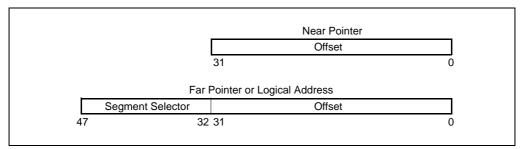

- Segmented memory model Memory appears to a program as a group of independent address spaces called segments. Code, data, and stacks are typically contained in separate segments. To address a byte in a segment, a program issues a logical address. This consists of a segment selector and an offset (logical addresses are often referred to as far pointers). The segment selector identifies the segment to be accessed and the offset identifies a byte in the address space of the segment. Programs running on an IA-32 processor can address up to 16,383 segments of different sizes and types, and each segment can be as large as 2<sup>32</sup> bytes.

Internally, all the segments that are defined for a system are mapped into the processor's linear address space. To access a memory location, the processor thus translates each logical address into a linear address. This translation is transparent to the application program.

The primary reason for using segmented memory is to increase the reliability of programs and systems. For example, placing a program's stack in a separate

segment prevents the stack from growing into the code or data space and overwriting instructions or data, respectively.

Real-address mode memory model — This is the memory model for the Intel 8086 processor. It is supported to provide compatibility with existing programs written to run on the Intel 8086 processor. The real-address mode uses a specific implementation of segmented memory in which the linear address space for the program and the operating system/executive consists of an array of segments of up to 64 KBytes in size each. The maximum size of the linear address space in real-address mode is 2<sup>20</sup> bytes.

See also: Chapter 17, "8086 Emulation," Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

Figure 3-3. Three Memory Management Models

# 3.3.2 Paging and Virtual Memory

With the flat or the segmented memory model, linear address space is mapped into the processor's physical address space either directly or through paging. When using direct mapping (paging disabled), each linear address has a one-to-one correspondence with a physical address. Linear addresses are sent out on the processor's address lines without translation.

When using the IA-32 architecture's paging mechanism (paging enabled), linear address space is divided into pages which are mapped to virtual memory. The pages of virtual memory are then mapped as needed into physical memory. When an operating system or executive uses paging, the paging mechanism is transparent to an application program. All that the application sees is linear address space.

In addition, IA-32 architecture's paging mechanism includes extensions that support:

- Page Address Extensions (PAE) to address physical address space greater than 4 GBytes.

- Page Size Extensions (PSE) to map linear address to physical address in 4-MBytes pages.

See also: Chapter 3, "Protected-Mode Memory Management," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

## 3.3.3 Memory Organization in 64-Bit Mode

Intel 64 architecture supports physical address space greater than 64 GBytes; the actual physical address size of IA-32 processors is implementation specific. In 64-bit mode, there is architectural support for 64-bit linear address space. However, processors supporting Intel 64 architecture may implement less than 64-bits (see Section 3.3.7.1). The linear address space is mapped into the processor physical address space through the PAE paging mechanism.

## 3.3.4 Modes of Operation vs. Memory Model

When writing code for an IA-32 or Intel 64 processor, a programmer needs to know the operating mode the processor is going to be in when executing the code and the memory model being used. The relationship between operating modes and memory models is as follows:

• **Protected mode** — When in protected mode, the processor can use any of the memory models described in this section. (The real-addressing mode memory model is ordinarily used only when the processor is in the virtual-8086 mode.) The memory model used depends on the design of the operating system or executive. When multitasking is implemented, individual tasks can use different memory models.

- **Real-address mode** When in real-address mode, the processor only supports the real-address mode memory model.

- **System management mode** When in SMM, the processor switches to a separate address space, called the system management RAM (SMRAM). The memory model used to address bytes in this address space is similar to the real-address mode model. See Chapter 26, "System Management," in the *Intel®* 64 and IA-32 Architectures Software Developer's Manual, Volume 3B, for more information on the memory model used in SMM.

- **Compatibility mode** Software that needs to run in compatibility mode should observe the same memory model as those targeted to run in 32-bit protected mode. The effect of segmentation is the same as it is in 32-bit protected mode semantics.

- **64-bit mode** Segmentation is generally (but not completely) disabled, creating a flat 64-bit linear-address space. Specifically, the processor treats the segment base of CS, DS, ES, and SS as zero in 64-bit mode (this makes a linear address equal an effective address). Segmented and real address modes are not available in 64-bit mode.

## 3.3.5 32-Bit and 16-Bit Address and Operand Sizes

IA-32 processors in protected mode can be configured for 32-bit or 16-bit address and operand sizes. With 32-bit address and operand sizes, the maximum linear address or segment offset is FFFFFFFH ( $2^{32}$ -1); operand sizes are typically 8 bits or 32 bits. With 16-bit address and operand sizes, the maximum linear address or segment offset is FFFFH ( $2^{16}$ -1); operand sizes are typically 8 bits or 16 bits.

When using 32-bit addressing, a logical address (or far pointer) consists of a 16-bit segment selector and a 32-bit offset; when using 16-bit addressing, an address consists of a 16-bit segment selector and a 16-bit offset.

Instruction prefixes allow temporary overrides of the default address and/or operand sizes from within a program.

When operating in protected mode, the segment descriptor for the currently executing code segment defines the default address and operand size. A segment descriptor is a system data structure not normally visible to application code. Assembler directives allow the default addressing and operand size to be chosen for a program. The assembler and other tools then set up the segment descriptor for the code segment appropriately.

When operating in real-address mode, the default addressing and operand size is 16 bits. An address-size override can be used in real-address mode to enable 32-bit addressing. However, the maximum allowable 32-bit linear address is still 000FFFFH (2<sup>20</sup>-1).

## 3.3.6 Extended Physical Addressing in Protected Mode

Beginning with P6 family processors, the IA-32 architecture supports addressing of up to 64 GBytes (2<sup>36</sup> bytes) of physical memory. A program or task could not address locations in this address space directly. Instead, it addresses individual linear address spaces of up to 4 GBytes that mapped to 64-GByte physical address space through a virtual memory management mechanism. Using this mechanism, an operating system can enable a program to switch 4-GByte linear address spaces within 64-GByte physical address space.

The use of extended physical addressing requires the processor to operate in protected mode and the operating system to provide a virtual memory management system. See "36-Bit Physical Addressing Using the PAE Paging Mechanism" in Chapter 3, "Protected-Mode Memory Management," of the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.*

## 3.3.7 Address Calculations in 64-Bit Mode

In most cases, 64-bit mode uses flat address space for code, data, and stacks. In 64-bit mode (if there is no address-size override), the size of effective address calculations is 64 bits. An effective-address calculation uses a 64-bit base and index registers and sign-extend displacements to 64 bits.

In the flat address space of 64-bit mode, linear addresses are equal to effective addresses because the base address is zero. In the event that FS or GS segments are used with a non-zero base, this rule does not hold. In 64-bit mode, the effective address components are added and the effective address is truncated (See for example the instruction LEA) before adding the full 64-bit segment base. The base is never truncated, regardless of addressing mode in 64-bit mode.

The instruction pointer is extended to 64 bits to support 64-bit code offsets. The 64-bit instruction pointer is called the RIP. Table 3-1 shows the relationship between RIP, EIP, and IP.

|                            | Bits 63:32     | Bits 31:16 | Bits 15:0 |

|----------------------------|----------------|------------|-----------|

| 16-bit instruction pointer | Not Modified   |            | IP        |

| 32-bit instruction pointer | Zero Extension | EIP        |           |

| 64-bit instruction pointer | RIP            |            |           |

#### Table 3-1. Instruction Pointer Sizes

Generally, displacements and immediates in 64-bit mode are not extended to 64 bits. They are still limited to 32 bits and sign-extended during effective-address calculations. In 64-bit mode, however, support is provided for 64-bit displacement and immediate forms of the MOV instruction.

All 16-bit and 32-bit address calculations are zero-extended in IA-32e mode to form 64-bit addresses. Address calculations are first truncated to the effective address

size of the current mode (64-bit mode or compatibility mode), as overridden by any address-size prefix. The result is then zero-extended to the full 64-bit address width. Because of this, 16-bit and 32-bit applications running in compatibility mode can access only the low 4 GBytes of the 64-bit mode effective addresses. Likewise, a 32-bit address generated in 64-bit mode can access only the low 4 GBytes of the 64-bit mode effective addresses of the 64-bit mode effective addresses.

#### 3.3.7.1 Canonical Addressing

In 64-bit mode, an address is considered to be in canonical form if address bits 63 through to the most-significant implemented bit by the microarchitecture are set to either all ones or all zeros.

Intel 64 architecture defines a 64-bit linear address. Implementations can support less. The first implementation of IA-32 processors with Intel 64 architecture supports a 48-bit linear address. This means a canonical address must have bits 63 through 48 set to zeros or ones (depending on whether bit 47 is a zero or one).

Although implementations may not use all 64 bits of the linear address, they should check bits 63 through the most-significant implemented bit to see if the address is in canonical form. If a linear-memory reference is not in canonical form, the implementation should generate an exception. In most cases, a general-protection exception (#GP) is generated. However, in the case of explicit or implied stack references, a stack fault (#SS) is generated.

Instructions that have implied stack references, by default, use the SS segment register. These include PUSH/POP-related instructions and instructions using RSP/RBP as base registers. In these cases, the canonical fault is #SF.

If an instruction uses base registers RSP/RBP and uses a segment override prefix to specify a non-SS segment, a canonical fault generates a #GP (instead of an #SF). In 64-bit mode, only FS and GS segment-overrides are applicable in this situation. Other segment override prefixes (CS, DS, ES and SS) are ignored. Note that this also means that an SS segment-override applied to a "non-stack" register reference is ignored. Such a sequence still produces a #GP for a canonical fault (and not an #SF).

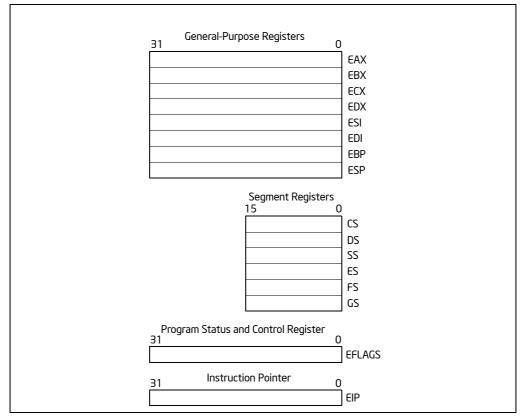

# 3.4 BASIC PROGRAM EXECUTION REGISTERS

IA-32 architecture provides 16 basic program execution registers for use in general system and application programing (see Figure 3-4). These registers can be grouped as follows:

- **General-purpose registers**. These eight registers are available for storing operands and pointers.

- Segment registers. These registers hold up to six segment selectors.

- **EFLAGS (program status and control) register**. The EFLAGS register report on the status of the program being executed and allows limited (application-program level) control of the processor.

- **EIP (instruction pointer) register**. The EIP register contains a 32-bit pointer to the next instruction to be executed.

## 3.4.1 General-Purpose Registers

The 32-bit general-purpose registers EAX, EBX, ECX, EDX, ESI, EDI, EBP, and ESP are provided for holding the following items:

- Operands for logical and arithmetic operations

- Operands for address calculations

- Memory pointers

Although all of these registers are available for general storage of operands, results, and pointers, caution should be used when referencing the ESP register. The ESP register holds the stack pointer and as a general rule should not be used for another purpose.

Many instructions assign specific registers to hold operands. For example, string instructions use the contents of the ECX, ESI, and EDI registers as operands. When using a segmented memory model, some instructions assume that pointers in certain registers are relative to specific segments. For instance, some instructions assume that a pointer in the EBX register points to a memory location in the DS segment.

Figure 3-4. General System and Application Programming Registers

The special uses of general-purpose registers by instructions are described in Chapter 5, "Instruction Set Summary," in this volume. See also: Chapter 3 and Chapter 4 of *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volumes 2A & 2B.* The following is a summary of special uses:

- EAX Accumulator for operands and results data

- **EBX** Pointer to data in the DS segment

- ECX Counter for string and loop operations

- EDX I/O pointer

- **ESI** Pointer to data in the segment pointed to by the DS register; source pointer for string operations

- **EDI** Pointer to data (or destination) in the segment pointed to by the ES register; destination pointer for string operations

- **ESP** Stack pointer (in the SS segment)

• **EBP** — Pointer to data on the stack (in the SS segment)

As shown in Figure 3-5, the lower 16 bits of the general-purpose registers map directly to the register set found in the 8086 and Intel 286 processors and can be referenced with the names AX, BX, CX, DX, BP, SI, DI, and SP. Each of the lower two bytes of the EAX, EBX, ECX, and EDX registers can be referenced by the names AH, BH, CH, and DH (high bytes) and AL, BL, CL, and DL (low bytes).

| Gene | eral-Purpo | se Regi | sters | 5  |   |        |        |

|------|------------|---------|-------|----|---|--------|--------|

| 31   | 16         | 15      | 87    |    | 0 | 16-bit | 32-bit |

|      |            | AH      |       | AL |   | AX     | EAX    |

|      |            | BH      |       | BL |   | BX     | EBX    |

|      |            | CH      |       | CL |   | CX     | ECX    |

|      |            | DH      |       | DL |   | DX     | EDX    |

|      |            |         | BP    |    |   |        | EBP    |

|      |            |         | SI    |    |   |        | ESI    |

|      |            |         | DI    |    |   |        | EDI    |

|      |            |         | SP    |    |   |        | ESP    |

#### 3.4.1.1 General-Purpose Registers in 64-Bit Mode

In 64-bit mode, there are 16 general purpose registers and the default operand size is 32 bits. However, general-purpose registers are able to work with either 32-bit or 64-bit operands. If a 32-bit operand size is specified: EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP, R8D - R15D are available. If a 64-bit operand size is specified: RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP, R8-R15 are available. R8D-R15D/R8-R15 represent eight new general-purpose registers. All of these registers can be accessed at the byte, word, dword, and qword level. REX prefixes are used to generate 64-bit operand sizes or to reference registers R8-R15.

Registers only available in 64-bit mode (R8-R15 and XMM8-XMM15) are preserved across transitions from 64-bit mode into compatibility mode then back into 64-bit mode. However, values of R8-R15 and XMM8-XMM15 are undefined after transitions from 64-bit mode through compatibility mode to legacy or real mode and then back through compatibility mode.

| Register Type        | Without REX                               | With REX                                              |

|----------------------|-------------------------------------------|-------------------------------------------------------|

| Byte Registers       | AL, BL, CL, DL, AH, BH, CH,<br>DH         | AL, BL, CL, DL, DIL, SIL, BPL, SPL,<br>R8L - R15L     |

| Word Registers       | AX, BX, CX, DX, DI, SI, BP, SP            | AX, BX, CX, DX, DI, SI, BP, SP, R8W -<br>R15W         |

| Doubleword Registers | EAX, EBX, ECX, EDX, EDI, ESI,<br>EBP, ESP | eax, ebx, ecx, edx, edi, esi, ebp,<br>esp, r8d - r15d |

| Quadword Registers   | N.A.                                      | RAX, RBX, RCX, RDX, RDI, RSI,<br>RBP, RSP, R8 - R15   |

#### Table 3-2. Addressable General Purpose Registers

In 64-bit mode, there are limitations on accessing byte registers. An instruction cannot reference legacy high-bytes (for example: AH, BH, CH, DH) and one of the new byte registers at the same time (for example: the low byte of the RAX register). However, instructions may reference legacy low-bytes (for example: AL, BL, CL or DL) and new byte registers at the same time (for example: the low byte of the R8 register, or RBP). The architecture enforces this limitation by changing high-byte references (AH, BH, CH, DH) to low byte references (BPL, SPL, DIL, SIL: the low 8 bits for RBP, RSP, RDI and RSI) for instructions using a REX prefix.

When in 64-bit mode, operand size determines the number of valid bits in the destination general-purpose register:

- 64-bit operands generate a 64-bit result in the destination general-purpose register.

- 32-bit operands generate a 32-bit result, zero-extended to a 64-bit result in the destination general-purpose register.

- 8-bit and 16-bit operands generate an 8-bit or 16-bit result. The upper 56 bits or 48 bits (respectively) of the destination general-purpose register are not be modified by the operation. If the result of an 8-bit or 16-bit operation is intended for 64-bit address calculation, explicitly sign-extend the register to the full 64-bits.

Because the upper 32 bits of 64-bit general-purpose registers are undefined in 32-bit modes, the upper 32 bits of any general-purpose register are not preserved when switching from 64-bit mode to a 32-bit mode (to protected mode or compatibility mode). Software must not depend on these bits to maintain a value after a 64-bit to 32-bit mode switch.

## 3.4.2 Segment Registers

The segment registers (CS, DS, SS, ES, FS, and GS) hold 16-bit segment selectors. A segment selector is a special pointer that identifies a segment in memory. To access a particular segment in memory, the segment selector for that segment must be present in the appropriate segment register.

When writing application code, programmers generally create segment selectors with assembler directives and symbols. The assembler and other tools then create the actual segment selector values associated with these directives and symbols. If writing system code, programmers may need to create segment selectors directly. See Chapter 3, "Protected-Mode Memory Management," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

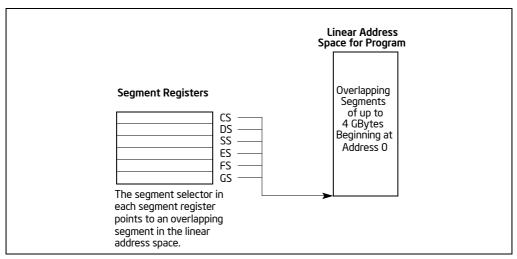

How segment registers are used depends on the type of memory management model that the operating system or executive is using. When using the flat (unsegmented) memory model, segment registers are loaded with segment selectors that point to overlapping segments, each of which begins at address 0 of the linear address space (see Figure 3-6). These overlapping segments then comprise the linear address space for the program. Typically, two overlapping segments are defined: one for code and another for data and stacks. The CS segment register points to the code segment and all the other segment registers point to the data and stack segment.

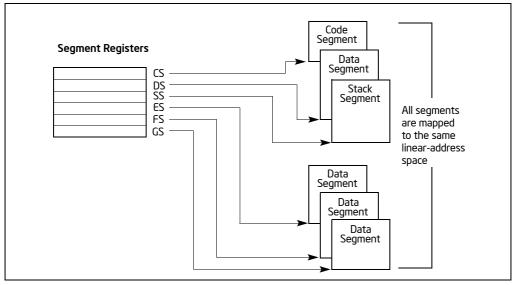

When using the segmented memory model, each segment register is ordinarily loaded with a different segment selector so that each segment register points to a different segment within the linear address space (see Figure 3-7). At any time, a program can thus access up to six segments in the linear address space. To access a segment not pointed to by one of the segment registers, a program must first load the segment selector for the segment to be accessed into a segment register.

Figure 3-6. Use of Segment Registers for Flat Memory Model

Figure 3-7. Use of Segment Registers in Segmented Memory Model

Each of the segment registers is associated with one of three types of storage: code, data, or stack. For example, the CS register contains the segment selector for the **code segment**, where the instructions being executed are stored. The processor fetches instructions from the code segment, using a logical address that consists of the segment selector in the CS register and the contents of the EIP register. The EIP register contains the offset within the code segment of the next instruction to be executed. The CS register cannot be loaded explicitly by an application program. Instead, it is loaded implicitly by instructions or internal processor operations that change program control (such as, procedure calls, interrupt handling, or task switching).

The DS, ES, FS, and GS registers point to four **data segments**. The availability of four data segments permits efficient and secure access to different types of data structures. For example, four separate data segments might be created: one for the data structures of the current module, another for the data exported from a higher-level module, a third for a dynamically created data structure, and a fourth for data shared with another program. To access additional data segments, the application program must load segment selectors for these segments into the DS, ES, FS, and GS registers, as needed.

The SS register contains the segment selector for the **stack segment**, where the procedure stack is stored for the program, task, or handler currently being executed. All stack operations use the SS register to find the stack segment. Unlike the CS register, the SS register can be loaded explicitly, which permits application programs to set up multiple stacks and switch among them.

See Section 3.3, "Memory Organization," for an overview of how the segment registers are used in real-address mode.

The four segment registers CS, DS, SS, and ES are the same as the segment registers found in the Intel 8086 and Intel 286 processors and the FS and GS registers were introduced into the IA-32 Architecture with the Intel386<sup>™</sup> family of processors.

#### 3.4.2.1 Segment Registers in 64-Bit Mode

In 64-bit mode: CS, DS, ES, SS are treated as if each segment base is 0, regardless of the value of the associated segment descriptor base. This creates a flat address space for code, data, and stack. FS and GS are exceptions. Both segment registers may be used as additional base registers in linear address calculations (in the addressing of local data and certain operating system data structures).

Even though segmentation is generally disabled, segment register loads may cause the processor to perform segment access assists. During these activities, enabled processors will still perform most of the legacy checks on loaded values (even if the checks are not applicable in 64-bit mode). Such checks are needed because a segment register loaded in 64-bit mode may be used by an application running in compatibility mode.

Limit checks for CS, DS, ES, SS, FS, and GS are disabled in 64-bit mode.

## 3.4.3 EFLAGS Register

The 32-bit EFLAGS register contains a group of status flags, a control flag, and a group of system flags. Figure 3-8 defines the flags within this register. Following initialization of the processor (either by asserting the RESET pin or the INIT pin), the state of the EFLAGS register is 0000002H. Bits 1, 3, 5, 15, and 22 through 31 of this register are reserved. Software should not use or depend on the states of any of these bits.

Some of the flags in the EFLAGS register can be modified directly, using specialpurpose instructions (described in the following sections). There are no instructions that allow the whole register to be examined or modified directly.

The following instructions can be used to move groups of flags to and from the procedure stack or the EAX register: LAHF, SAHF, PUSHF, PUSHFD, POPF, and POPFD. After the contents of the EFLAGS register have been transferred to the procedure stack or EAX register, the flags can be examined and modified using the processor's bit manipulation instructions (BT, BTS, BTR, and BTC).

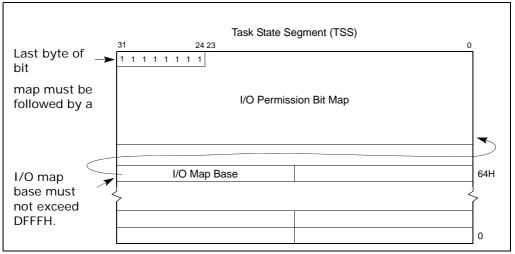

When suspending a task (using the processor's multitasking facilities), the processor automatically saves the state of the EFLAGS register in the task state segment (TSS) for the task being suspended. When binding itself to a new task, the processor loads the EFLAGS register with data from the new task's TSS.

When a call is made to an interrupt or exception handler procedure, the processor automatically saves the state of the EFLAGS registers on the procedure stack. When

an interrupt or exception is handled with a task switch, the state of the EFLAGS register is saved in the TSS for the task being suspended.

|                                                                                                                                                                                                                                                                              | 31 30                                                                                                                                                 | 29 28                             | 27 2                                                 | 6 25           | 24 23 | 8 22 | 21     | 20          | 19          | 18     | 17     | 16     | 15 | 14     | 13 12            | 11     | 10     | 9      | 8      | 7      | 6      | 5 | 4      | 3 | 2      | 1 | 0      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------|----------------|-------|------|--------|-------------|-------------|--------|--------|--------|----|--------|------------------|--------|--------|--------|--------|--------|--------|---|--------|---|--------|---|--------|

|                                                                                                                                                                                                                                                                              | 0 0                                                                                                                                                   | 0 0                               | 0 0                                                  | 0              | 0 0   | 0    | I<br>D | V<br>I<br>P | V<br>I<br>F | A<br>C | ∨<br>M | R<br>F | 0  | N<br>T | I<br>O<br>P<br>L | 0<br>F | D<br>F | l<br>F | T<br>F | S<br>F | Z<br>F | 0 | A<br>F | 0 | P<br>F | 1 | C<br>F |

| X ID Flag (IE<br>X Virtual Inte<br>X Alignment (<br>X Virtual-808)<br>X Resume Fl<br>X Nested Tas<br>X //O Privileg<br>S Overflow F<br>C Direction F<br>X Interrupt Er<br>X Trap Flag (<br>S Sign Flag (<br>S Zero Flag (<br>S Auxiliary Ca<br>S Parity Flag<br>S Carry Flag | errupt<br>rrupt F<br>Check<br>6 Moc<br>lag (R<br>sk (NT<br>e Leve<br>lag (C<br>lag (C<br>lag (C<br>nable<br>TF) —<br>SF) —<br>ZF) —<br>arry F<br>(PF) | Pen<br>Flag<br>(AC<br>le (V<br>F) | ding<br>(VIF<br>:) —<br>M) –<br>DPL)<br>(IF)<br>(IF) | (VI<br>) —<br> | P) -  |      |        |             |             |        |        |        |    |        |                  |        |        |        |        |        |        |   |        |   |        |   |        |

| S Indicates a<br>C Indicates a<br>X Indicates a                                                                                                                                                                                                                              | Conti                                                                                                                                                 | rol Fl                            | ag                                                   |                |       |      |        |             |             |        |        |        |    |        |                  |        |        |        |        |        |        |   |        |   |        |   |        |

| Reserve<br>Always s                                                                                                                                                                                                                                                          |                                                                                                                                                       |                                   |                                                      |                |       |      |        |             |             |        |        |        |    |        |                  |        |        |        |        |        |        |   |        |   |        |   |        |

#### Figure 3-8. EFLAGS Register

As the IA-32 Architecture has evolved, flags have been added to the EFLAGS register, but the function and placement of existing flags have remained the same from one family of the IA-32 processors to the next. As a result, code that accesses or modifies these flags for one family of IA-32 processors works as expected when run on later families of processors.

#### 3.4.3.1 Status Flags

The status flags (bits 0, 2, 4, 6, 7, and 11) of the EFLAGS register indicate the results of arithmetic instructions, such as the ADD, SUB, MUL, and DIV instructions. The status flag functions are:

**CF (bit 0) Carry flag** — Set if an arithmetic operation generates a carry or a borrow out of the most-significant bit of the result; cleared

otherwise. This flag indicates an overflow condition for unsigned-integer arithmetic. It is also used in multiple-precision arithmetic.

- **PF (bit 2) Parity flag** Set if the least-significant byte of the result contains an even number of 1 bits; cleared otherwise.

- AF (bit 4) Adjust flag Set if an arithmetic operation generates a carry or a borrow out of bit 3 of the result; cleared otherwise. This flag is used in binary-coded decimal (BCD) arithmetic.

- **ZF (bit 6) Zero flag** Set if the result is zero; cleared otherwise.

- **SF (bit 7)** Sign flag Set equal to the most-significant bit of the result, which is the sign bit of a signed integer. (0 indicates a positive value and 1 indicates a negative value.)

- **OF (bit 11) Overflow flag** Set if the integer result is too large a positive number or too small a negative number (excluding the sign-bit) to fit in the destination operand; cleared otherwise. This flag indicates an overflow condition for signed-integer (two's complement) arithmetic.

Of these status flags, only the CF flag can be modified directly, using the STC, CLC, and CMC instructions. Also the bit instructions (BT, BTS, BTR, and BTC) copy a specified bit into the CF flag.

The status flags allow a single arithmetic operation to produce results for three different data types: unsigned integers, signed integers, and BCD integers. If the result of an arithmetic operation is treated as an unsigned integer, the CF flag indicates an out-of-range condition (carry or a borrow); if treated as a signed integer (two's complement number), the OF flag indicates a carry or borrow; and if treated as a BCD digit, the AF flag indicates a carry or borrow. The SF flag indicates the sign of a signed integer. The ZF flag indicates either a signed- or an unsigned-integer zero.

When performing multiple-precision arithmetic on integers, the CF flag is used in conjunction with the add with carry (ADC) and subtract with borrow (SBB) instructions to propagate a carry or borrow from one computation to the next.

The condition instructions Jcc (jump on condition code cc), SETcc (byte set on condition code cc), LOOPcc, and CMOVcc (conditional move) use one or more of the status flags as condition codes and test them for branch, set-byte, or end-loop conditions.

## 3.4.3.2 DF Flag

The direction flag (DF, located in bit 10 of the EFLAGS register) controls string instructions (MOVS, CMPS, SCAS, LODS, and STOS). Setting the DF flag causes the string instructions to auto-decrement (to process strings from high addresses to low addresses). Clearing the DF flag causes the string instructions to auto-increment (process strings from low addresses to high addresses).

The STD and CLD instructions set and clear the DF flag, respectively.

### 3.4.3.3 System Flags and IOPL Field

The system flags and IOPL field in the EFLAGS register control operating-system or executive operations. **They should not be modified by application programs**. The functions of the system flags are as follows:

| TF (bit 8)        | <b>Trap flag</b> — Set to enable single-step mode for debugging; clear to disable single-step mode.                                                                                                                                                                                                                                                                                            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IF (bit 9)        | <b>Interrupt enable flag</b> — Controls the response of the processor to maskable interrupt requests. Set to respond to maskable interrupts; cleared to inhibit maskable interrupts.                                                                                                                                                                                                           |

| IOPL (bits 12 and | <b>13)</b><br><b>I/O privilege level field</b> — Indicates the I/O privilege level of the currently running program or task. The current privilege level (CPL) of the currently running program or task must be less than or equal to the I/O privilege level to access the I/O address space. This field can only be modified by the POPF and IRET instructions when operating at a CPL of 0. |

| NT (bit 14)       | <b>Nested task flag</b> — Controls the chaining of interrupted and called tasks. Set when the current task is linked to the previously executed task; cleared when the current task is not linked to another task.                                                                                                                                                                             |

| RF (bit 16)       | <b>Resume flag</b> — Controls the processor's response to debug exceptions.                                                                                                                                                                                                                                                                                                                    |

| VM (bit 17)       | <b>Virtual-8086 mode flag</b> — Set to enable virtual-8086 mode; clear to return to protected mode without virtual-8086 mode semantics.                                                                                                                                                                                                                                                        |

| AC (bit 18)       | <b>Alignment check flag</b> — Set this flag and the AM bit in the CR0 register to enable alignment checking of memory references; clear the AC flag and/or the AM bit to disable alignment checking.                                                                                                                                                                                           |

| VIF (bit 19)      | <b>Virtual interrupt flag</b> — Virtual image of the IF flag. Used in conjunction with the VIP flag. (To use this flag and the VIP flag the virtual mode extensions are enabled by setting the VME flag in control register CR4.)                                                                                                                                                              |

| VIP (bit 20)      | <b>Virtual interrupt pending flag</b> — Set to indicate that an interrupt is pending; clear when no interrupt is pending. (Software sets and clears this flag; the processor only reads it.) Used in conjunction with the VIF flag.                                                                                                                                                            |

| ID (bit 21)       | <b>Identification flag</b> — The ability of a program to set or clear this flag indicates support for the CPUID instruction.                                                                                                                                                                                                                                                                   |

For a detailed description of these flags: see Chapter 3, "Protected-Mode Memory Management," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

#### 3.4.3.4 RFLAGS Register in 64-Bit Mode

In 64-bit mode, EFLAGS is extended to 64 bits and called RFLAGS. The upper 32 bits of RFLAGS register is reserved. The lower 32 bits of RFLAGS is the same as EFLAGS.

# 3.5 INSTRUCTION POINTER

The instruction pointer (EIP) register contains the offset in the current code segment for the next instruction to be executed. It is advanced from one instruction boundary to the next in straight-line code or it is moved ahead or backwards by a number of instructions when executing JMP, Jcc, CALL, RET, and IRET instructions.

The EIP register cannot be accessed directly by software; it is controlled implicitly by control-transfer instructions (such as JMP, J*cc*, CALL, and RET), interrupts, and exceptions. The only way to read the EIP register is to execute a CALL instruction and then read the value of the return instruction pointer from the procedure stack. The EIP register can be loaded indirectly by modifying the value of a return instruction pointer on the procedure stack and executing a return instruction (RET or IRET). See Section 6.2.4.2, "Return Instruction Pointer."

All IA-32 processors prefetch instructions. Because of instruction prefetching, an instruction address read from the bus during an instruction load does not match the value in the EIP register. Even though different processor generations use different prefetching mechanisms, the function of the EIP register to direct program flow remains fully compatible with all software written to run on IA-32 processors.

## 3.5.1 Instruction Pointer in 64-Bit Mode

In 64-bit mode, the RIP register becomes the instruction pointer. This register holds the 64-bit offset of the next instruction to be executed. 64-bit mode also supports a technique called RIP-relative addressing. Using this technique, the effective address is determined by adding a displacement to the RIP of the next instruction.

# **3.6 OPERAND-SIZE AND ADDRESS-SIZE ATTRIBUTES**

When the processor is executing in protected mode, every code segment has a default operand-size attribute and address-size attribute. These attributes are selected with the D (default size) flag in the segment descriptor for the code segment (see Chapter 3, "Protected-Mode Memory Management," in the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A*). When the D flag is set, the 32-bit operand-size and address-size attributes are selected; when the flag is clear, the 16-bit size attributes are selected. When the processor is executing in real-address mode, virtual-8086 mode, or SMM, the default operand-size and address-size attributes are selected.

This chapter introduces data types defined for the Intel 64 and IA-32 architectures. A section at the end of this chapter describes the real-number and floating-point concepts used in x87 FPU, SSE, SSE2, SSE3 and SSSE3 extensions.

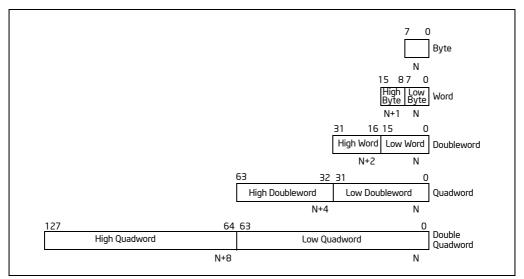

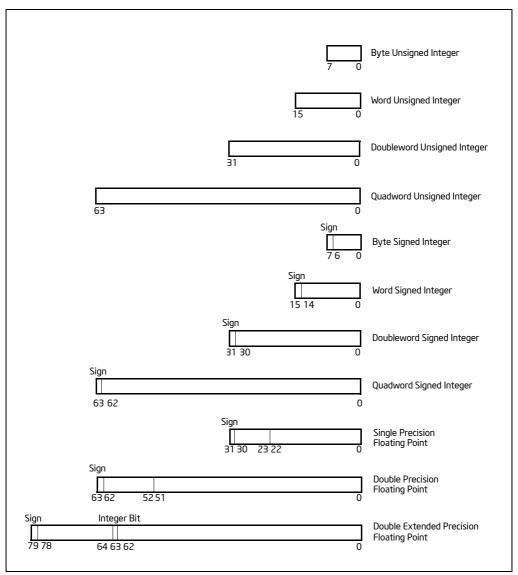

# 4.1 FUNDAMENTAL DATA TYPES

The fundamental data types are bytes, words, doublewords, quadwords, and double quadwords (see Figure 4-1). A byte is eight bits, a word is 2 bytes (16 bits), a doubleword is 4 bytes (32 bits), a quadword is 8 bytes (64 bits), and a double quadword is 16 bytes (128 bits). A subset of the IA-32 architecture instructions operates on these fundamental data types without any additional operand typing.

Figure 4-1. Fundamental Data Types

The quadword data type was introduced into the IA-32 architecture in the Intel486 processor; the double quadword data type was introduced in the Pentium III processor with the SSE extensions.

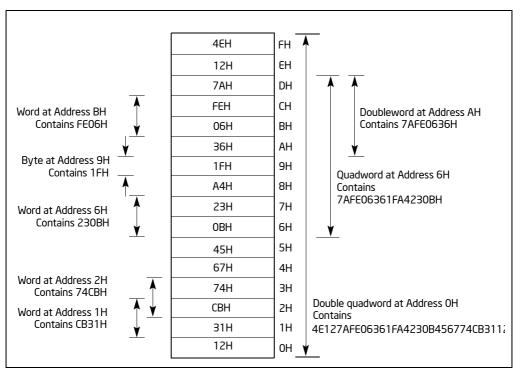

Figure 4-2 shows the byte order of each of the fundamental data types when referenced as operands in memory. The low byte (bits 0 through 7) of each data type occupies the lowest address in memory and that address is also the address of the operand.

Figure 4-2. Bytes, Words, Doublewords, Quadwords, and Double Quadwords in Memory

# 4.1.1 Alignment of Words, Doublewords, Quadwords, and Double Quadwords

Words, doublewords, and quadwords do not need to be aligned in memory on natural boundaries. The natural boundaries for words, double words, and quadwords are even-numbered addresses, addresses evenly divisible by four, and addresses evenly divisible by eight, respectively. However, to improve the performance of programs, data structures (especially stacks) should be aligned on natural boundaries whenever possible. The reason for this is that the processor requires two memory accesses to make an unaligned memory access; aligned accesses require only one memory access. A word or doubleword operand that crosses a 4-byte boundary or a quadword operand that crosses an 8-byte boundary is considered unaligned and requires two separate memory bus cycles for access.

Some instructions that operate on double quadwords require memory operands to be aligned on a natural boundary. These instructions generate a general-protection exception (#GP) if an unaligned operand is specified. A natural boundary for a double quadword is any address evenly divisible by 16. Other instructions that operate on double quadwords permit unaligned access (without generating a general-protection

exception). However, additional memory bus cycles are required to access unaligned data from memory.

# 4.2 NUMERIC DATA TYPES

Although bytes, words, and doublewords are fundamental data types, some instructions support additional interpretations of these data types to allow operations to be performed on numeric data types (signed and unsigned integers, and floating-point numbers). See Figure 4-3.

Figure 4-3. Numeric Data Types

## 4.2.1 Integers

The Intel 64 and IA-32 architectures define two types of integers: unsigned and signed. Unsigned integers are ordinary binary values ranging from 0 to the maximum positive number that can be encoded in the selected operand size. Signed integers

are two's complement binary values that can be used to represent both positive and negative integer values.

Some integer instructions (such as the ADD, SUB, PADDB, and PSUBB instructions) operate on either unsigned or signed integer operands. Other integer instructions (such as IMUL, MUL, IDIV, DIV, FIADD, and FISUB) operate on only one integer type.

The following sections describe the encodings and ranges of the two types of integers.

#### 4.2.1.1 Unsigned Integers

Unsigned integers are unsigned binary numbers contained in a byte, word, doubleword, and quadword. Their values range from 0 to 255 for an unsigned byte integer, from 0 to 65,535 for an unsigned word integer, from 0 to  $2^{32} - 1$  for an unsigned doubleword integer, and from 0 to  $2^{64} - 1$  for an unsigned quadword integer. Unsigned integers are sometimes referred to as **ordinals**.

#### 4.2.1.2 Signed Integers

Signed integers are signed binary numbers held in a byte, word, doubleword, or quadword. All operations on signed integers assume a two's complement representation. The sign bit is located in bit 7 in a byte integer, bit 15 in a word integer, bit 31 in a doubleword integer, and bit 63 in a quadword integer (see the signed integer encodings in Table 4-1).

|                | Class    | Two's Complem                                                                                          | ent Encoding                                                                                                                                                                                       |

|----------------|----------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |          | Sign                                                                                                   |                                                                                                                                                                                                    |

| Positive       | Largest  | 0                                                                                                      | 1111                                                                                                                                                                                               |

|                |          |                                                                                                        |                                                                                                                                                                                                    |

|                |          |                                                                                                        |                                                                                                                                                                                                    |

|                | Smallest | 0                                                                                                      | 0001                                                                                                                                                                                               |

| Zero           |          | 0                                                                                                      | 0000                                                                                                                                                                                               |

| Negative       | Smallest | 1                                                                                                      | 1111                                                                                                                                                                                               |

|                |          |                                                                                                        |                                                                                                                                                                                                    |

|                |          |                                                                                                        |                                                                                                                                                                                                    |

|                | Largest  | 1                                                                                                      | 0000                                                                                                                                                                                               |

| Integer indefi | nite     | 1                                                                                                      | 0000                                                                                                                                                                                               |

|                |          | Signed Byte Integer:<br>Signed Word Integer:<br>Signed Doubleword Integer:<br>Signed Quadword Integer: | $\begin{array}{c} \leftarrow 7 \text{ bits} \rightarrow \\ \leftarrow 15 \text{ bits} \rightarrow \\ \leftarrow 31 \text{ bits} \rightarrow \\ \leftarrow 63 \text{ bits} \rightarrow \end{array}$ |

#### Table 4-1. Signed Integer Encodings

The sign bit is set for negative integers and cleared for positive integers and zero. Integer values range from -128 to +127 for a byte integer, from -32,768 to +32,767 for a word integer, from  $-2^{31}$  to  $+2^{31} - 1$  for a doubleword integer, and from  $-2^{63}$  to  $+2^{63} - 1$  for a quadword integer.

When storing integer values in memory, word integers are stored in 2 consecutive bytes; doubleword integers are stored in 4 consecutive bytes; and quadword integers are stored in 8 consecutive bytes.

The integer indefinite is a special value that is sometimes returned by the x87 FPU when operating on integer values. For more information, see Section 8.2.1, "Indefinites."

# 4.2.2 Floating-Point Data Types

The IA-32 architecture defines and operates on three floating-point data types: single-precision floating-point, double-precision floating-point, and double-extended precision floating-point (see Figure 4-3). The data formats for these data types correspond directly to formats specified in the IEEE Standard 754 for Binary Floating-Point Arithmetic.

Table 4-2 gives the length, precision, and approximate normalized range that can be represented by each of these data types. Denormal values are also supported in each of these types.

| Data Type                    | Length | Precision | Approximate Normalized Range              |                                                     |  |  |  |  |  |  |

|------------------------------|--------|-----------|-------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|

|                              |        | (Bits)    | Binary                                    | Decimal                                             |  |  |  |  |  |  |

| Single Precision             | 32     | 24        | 2 <sup>-126</sup> to 2 <sup>127</sup>     | $1.18 \times 10^{-38}$ to $3.40 \times 10^{38}$     |  |  |  |  |  |  |

| Double Precision             | 64     | 53        | 2 <sup>-1022</sup> to 2 <sup>1023</sup>   | $2.23\times10^{-308}$ to $1.79\times10^{308}$       |  |  |  |  |  |  |

| Double Extended<br>Precision | 80     | 64        | 2 <sup>-16382</sup> to 2 <sup>16383</sup> | $3.37 \times 10^{-4932}$ to $1.18 \times 10^{4932}$ |  |  |  |  |  |  |

Table 4-2. Length, Precision, and Range of Floating-Point Data Types

#### NOTE

Section 4.8, "Real Numbers and Floating-Point Formats," gives an overview of the IEEE Standard 754 floating-point formats and defines the terms integer bit, QNaN, SNaN, and denormal value.

Table 4-3 shows the floating-point encodings for zeros, denormalized finite numbers, normalized finite numbers, infinites, and NaNs for each of the three floating-point data types. It also gives the format for the QNaN floating-point indefinite value. (See Section 4.8.3.7, "QNaN Floating-Point Indefinite," for a discussion of the use of the QNaN floating-point indefinite value.)

For the single-precision and double-precision formats, only the fraction part of the significand is encoded. The integer is assumed to be 1 for all numbers except 0 and denormalized finite numbers. For the double extended-precision format, the integer is contained in bit 63, and the most-significant fraction bit is bit 62. Here, the integer is explicitly set to 1 for normalized numbers, infinities, and NaNs, and to 0 for zero and denormalized numbers.

|          | Class                                                 | Sign | Biased Exponent                                                                                                                                            | Significand          |                                                                                                                                                           |  |  |  |  |  |

|----------|-------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          |                                                       |      |                                                                                                                                                            | Integer <sup>1</sup> | Fraction                                                                                                                                                  |  |  |  |  |  |

| Positive | +∞                                                    | 0    | 1                                                                                                                                                          | 0000                 |                                                                                                                                                           |  |  |  |  |  |

|          | +Normals                                              | 1    | 1111                                                                                                                                                       |                      |                                                                                                                                                           |  |  |  |  |  |

|          |                                                       | •    |                                                                                                                                                            | •                    |                                                                                                                                                           |  |  |  |  |  |

|          |                                                       | 0    | 0001                                                                                                                                                       | 1                    | 0000                                                                                                                                                      |  |  |  |  |  |

|          | +Denormals                                            | 0    | 0000                                                                                                                                                       | 0                    | 11.11                                                                                                                                                     |  |  |  |  |  |

|          |                                                       | •    |                                                                                                                                                            | •                    |                                                                                                                                                           |  |  |  |  |  |

|          |                                                       | 0    | 0000                                                                                                                                                       | 0                    | 0001                                                                                                                                                      |  |  |  |  |  |

|          | +Zero                                                 | 0    | 0000                                                                                                                                                       | 0                    | 0000                                                                                                                                                      |  |  |  |  |  |

| Negative | –Zего                                                 | 1    | 0000                                                                                                                                                       | 0                    | 0000                                                                                                                                                      |  |  |  |  |  |

|          | -Denormals                                            | 1    | 0000                                                                                                                                                       | 0                    | 0001                                                                                                                                                      |  |  |  |  |  |

|          |                                                       | •    |                                                                                                                                                            |                      |                                                                                                                                                           |  |  |  |  |  |

|          |                                                       | 1    | 0000                                                                                                                                                       | 0                    | 1111                                                                                                                                                      |  |  |  |  |  |

|          | -Normals                                              | 1    | 0001                                                                                                                                                       | 1                    | 0000                                                                                                                                                      |  |  |  |  |  |

|          |                                                       |      |                                                                                                                                                            |                      |                                                                                                                                                           |  |  |  |  |  |

|          |                                                       | 1    | 1110                                                                                                                                                       | 1                    | 1111                                                                                                                                                      |  |  |  |  |  |

|          | -∞-                                                   | 1    | 1111                                                                                                                                                       | 1                    | 0000                                                                                                                                                      |  |  |  |  |  |

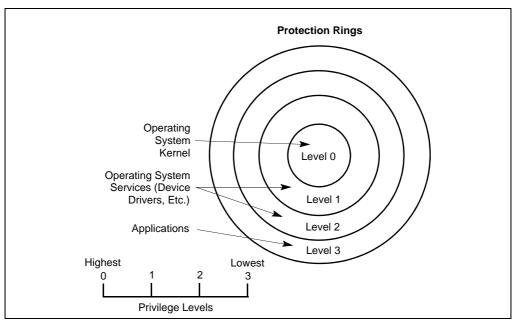

| NaNs     | SNaN                                                  | Х    | 1111                                                                                                                                                       | 1                    | 0XXX <sup>2</sup>                                                                                                                                         |  |  |  |  |  |